優(yōu)化PCB布線減少串?dāng)_的解決方案

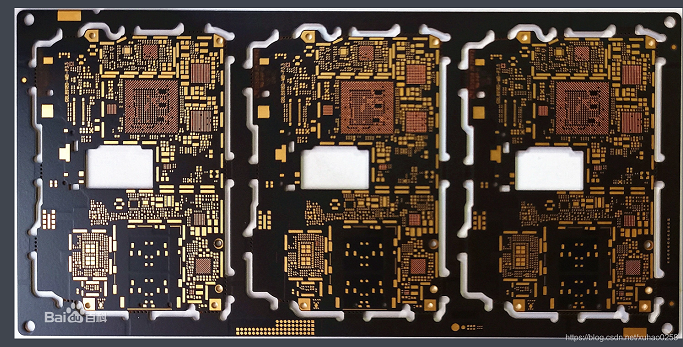

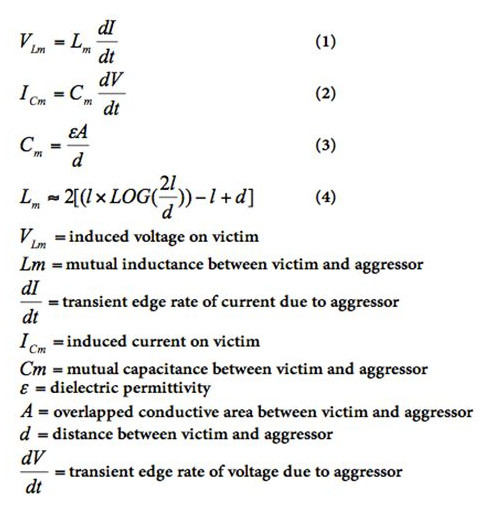

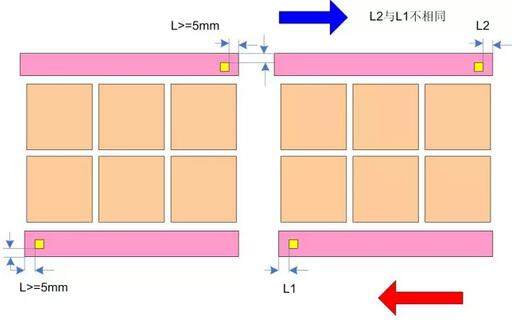

設(shè)計(jì)人員必須小心的規(guī)劃 PCB 的高速串行信號(hào)走線�,以便盡可能減少線對間串?dāng)_,防止信道傳輸對數(shù)據(jù)造成破壞��,本文介紹了優(yōu)化信號(hào)布線以顯著減少串?dāng)_的方法����。I.序言如今,各種便攜式計(jì)算設(shè)備都應(yīng)用了密集的印刷電路板(PCB)設(shè)計(jì)�,并使用了多個(gè)高速數(shù)字通信協(xié)議,例如 PCIe���、USB 和 SATA,這些高速數(shù)字協(xié)議支持高達(dá) Gb 的數(shù)據(jù)吞吐速率并具有數(shù)百毫伏的差分幅度��。入侵(aggressor)信號(hào)與受害(

設(shè)計(jì)人員必須小心的規(guī)劃 PCB 的高速串行信號(hào)走線�����,以便盡可能減少線對間串?dāng)_�,防止信道傳輸對數(shù)據(jù)造成破壞�����,本文介紹了優(yōu)化信號(hào)布線以顯著減少串?dāng)_的方法。